### **General Description**

The MAX3892 serializer is ideal for converting 4-bitwide, 622Mbps parallel data to 2.5Gbps serial data in DWDM and SONET/SDH applications. A 4 × 4-bit FIFO allows for any static delay between the parallel output clock and parallel input clock. Delay variation up to a unit interval (UI) is allowed after reset. A fully integrated phase-locked loop (PLL) synthesizes an internal 2.5GHz serial clock from a 622MHz, 155.5MHz, 77.8MHz, or 38.9MHz reference clock. A selectable dual VCO allows excellent jitter performance at both SONET and forward-error correction (FEC) data rates.

Operating from a single 3.3V supply, this device accepts low-voltage differential-signal (LVDS) clock and data inputs for interfacing with high-speed digital circuitry, and delivers current-mode logic (CML) serial data and clock outputs. A loopback data output is provided to facilitate system diagnostic testing. The MAX3892 is available in the extended temperature range (-40°C to +85°C) in a 44-pin QFN package.

### Applications

SONET/SDH OC-48 Transmission Systems WDM Transponders Add/Drop Multiplexers Dense Digital Cross-Connects Backplane Interconnects

## Single +3.3V Supply

- ♦ 455mW Power Consumption

- 1.4ps<sub>RMS</sub> Maximum Jitter Generation

- ♦ 4 × 4-Bit FIFO Input Buffer

- 622Mbps/666Mbps Parallel to 2.5Gbps/2.7Gbps Serial Conversion

- ♦ 622MHz/667MHz or 311MHz/333MHz Clock Input

- On-Chip Clock Synthesizer

- Multiple Clock Reference Frequencies: (622.08MHz, 155.52MHz, 77.76MHz, 38.88MHz) or (666.51MHz, 166.63MHz, 83.31MHz, 41.66MHz)

- LVDS Parallel Clock and Data Inputs

- CML Serial Data and Clock Outputs

- Additional CML Output for System Loopback Testing

### **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |  |

|------------|----------------|-------------|--|

| MAX3892EGH | -40°C to +85°C | 44 QFN-EP*  |  |

\*EP = exposed pad

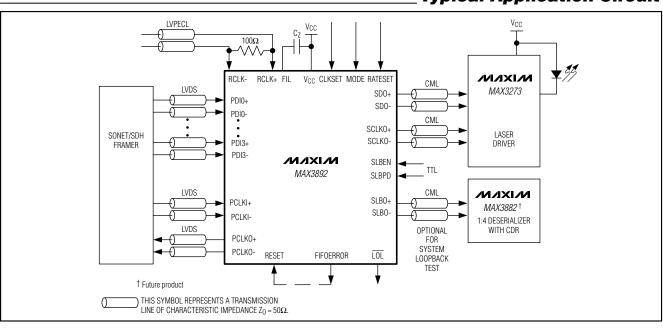

### **Typical Application Circuit**

###

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

Features

# **MAX3892**

### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage V<sub>CC</sub>, VCCO, VCCVCO .....-0.5V to +5V All Inputs and FIL .....-0.5V to (V<sub>CC</sub> + 0.5V) LVDS Output Voltage (PCLKO±)....-0.5V to (V<sub>CC</sub> + 0.5V) CML Output Current (SDO±, SCLKO±, SLBO±).....22mA Continuous Power Dissipation (T<sub>A</sub> = +85°C) 44-Pin QFN (derate 25mW/°C above +85°C) ......1625mW

| Operating Temperature Range       |                |

|-----------------------------------|----------------|

| Storage Temperature Range         | 55°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3V$ , differential LVDS load =  $100\Omega \pm 1\%$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                                         | SYMBOL              | CONDITIONS                 | MIN                       | ТҮР                   | MAX                       | UNITS |

|-----------------------------------------------------------------------------------|---------------------|----------------------------|---------------------------|-----------------------|---------------------------|-------|

| Supply Current                                                                    | ICC                 | (Note 2)                   |                           | 138                   | 190                       | mA    |

| LVDS INPUT SPECIFICATIONS (F                                                      | PDI[30]±, F         | CLKI±)                     |                           |                       |                           |       |

| Input Voltage Range                                                               | VI                  |                            | 0                         |                       | 2400                      | mV    |

| Differential Input Voltage                                                        | IVIDI               |                            | 100                       |                       |                           | mV    |

| Input Common-Mode Current                                                         |                     | LVDS input $V_{OS} = 1.2V$ |                           | 61                    |                           | μA    |

| Threshold Hysteresis                                                              |                     |                            |                           | 45                    |                           | mV    |

| Differential Input Resistance                                                     | R <sub>IN</sub>     |                            | 83                        | 100                   | 117                       | Ω     |

| LVPECL INPUT SPECIFICATIONS                                                       | (RCLK±)             |                            |                           |                       |                           |       |

| Input High Voltage                                                                | VIH                 |                            | V <sub>CC</sub> -<br>1.16 |                       | V <sub>CC</sub> -<br>0.88 | V     |

| Input Low Voltage                                                                 | VIL                 |                            | V <sub>CC</sub> -<br>1.81 |                       | V <sub>CC</sub> -<br>1.48 | V     |

| Input Bias Voltage                                                                |                     |                            |                           | V <sub>CC</sub> - 1.3 |                           | V     |

| Single-Ended Input Resistance                                                     |                     |                            |                           | >1.0                  |                           | kΩ    |

| Differential Input Voltage Swing                                                  |                     |                            | 300                       |                       | 1900                      | mVp-p |

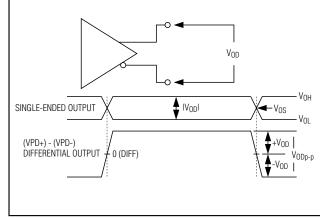

| LVDS OUTPUT SPECIFICATIONS                                                        | (PCLKO±)            |                            |                           |                       |                           |       |

| Output High Voltage                                                               | VOH                 |                            |                           |                       | 1.475                     | V     |

| Output Low Voltage                                                                | V <sub>OL</sub>     |                            | 0.925                     |                       |                           | V     |

| Differential Output Voltage                                                       | IV <sub>OD</sub> I  |                            | 250                       |                       | 400                       | mV    |

| Change in Magnitude of<br>Differential Output Voltage for<br>Complementary States | ΔIV <sub>OD</sub> I |                            |                           |                       | 25                        | mV    |

| Offset Output Voltage                                                             |                     |                            | 1.125                     |                       | 1.275                     | V     |

| Change in Magnitude of Output<br>Offset Voltage for Complementary<br>States       | ΔIV <sub>OS</sub> I |                            |                           |                       | 25                        | mV    |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.$  Typical values are at  $V_{CC} = +3.3V$ , differential LVDS load =  $100\Omega \pm 1\%$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                      | SYMBOL                            | CONDITIONS                     | MIN  | ТҮР                   | MAX              | UNITS |  |

|--------------------------------|-----------------------------------|--------------------------------|------|-----------------------|------------------|-------|--|

| Differential Output Resistance |                                   |                                | 80   |                       | 140              | Ω     |  |

| Output Current                 |                                   | Shorted together               |      |                       | 12               | mA    |  |

| Output Current                 |                                   | Shorted to ground              |      |                       | 40               | mA    |  |

| CML OUTPUT SPECIFICATIONS      | (SDO±, SCL                        | .KO±, SLBO±)                   |      |                       |                  |       |  |

| Differential Output            |                                   | $R_L = 100\Omega$ differential | 640  | 800                   | 1000             | mVp-p |  |

| Differential Output Resistance |                                   |                                | 83   | 100                   | 117              | Ω     |  |

| Output Common-Mode Voltage     |                                   | $R_L = 50\Omega$ to $V_{CC}$   |      | V <sub>CC</sub> - 0.2 |                  | V     |  |

| LVTTL SPECIFICATIONS (RESET    | , RATESET,                        | SLBEN, SLBPD FIFOERROR, LOL)   |      |                       |                  |       |  |

| Input High Voltage             | VIH                               |                                | 2.0  |                       |                  | V     |  |

| Input Low Voltage              | VIL                               |                                |      |                       | 0.8              | V     |  |

| Input High Current             | IIН                               |                                | -30  |                       | +10              | μΑ    |  |

| Input Low Current              | ١ <sub>١</sub> ٢                  |                                | -50  |                       | +10              | μA    |  |

| Output High Voltage            | VOH                               | I <sub>OH</sub> = 20µА         | 2.4  |                       | V <sub>C</sub> C | V     |  |

| Output Low Voltage             | VOL                               | I <sub>OL</sub> = 1mA          |      |                       | 0.4              | V     |  |

| PROGRAMMING INPUTS (CLKSE      | PROGRAMMING INPUTS (CLKSET, MODE) |                                |      |                       |                  |       |  |

| Input Current                  |                                   | Input = 0 or V <sub>CC</sub>   | -500 |                       | +500             | μΑ    |  |

### **AC ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +3.0V to +3.6V, T<sub>A</sub> = -40°C to +85°C. Typical values are at V<sub>CC</sub> = +3.3V, differential LVDS loads = 100 $\Omega$  ±1%, CML loads = 50 $\Omega$  ±1%, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 3)

| PARAMETER                                    | SYMBOL                          | CONDITIONS                         | MIN | ТҮР   | МАХ | UNITS |  |

|----------------------------------------------|---------------------------------|------------------------------------|-----|-------|-----|-------|--|

| PARALLEL INPUT SPECIFICATIONS (PDI±, PCLKI±) |                                 |                                    |     |       |     |       |  |

| Parallel Input Data Pata                     |                                 | RATESET = GND                      |     | 622   |     | Mhpa  |  |

| Parallel Input Data Rate                     |                                 | RATESET = $V_{CC}$                 |     | 666   |     | Mbps  |  |

| Parallal Input Clask Pata                    |                                 | MODE = OPEN or $V_{CC}$            |     | 622   |     | MHz   |  |

| Parallel Input Clock Rate                    |                                 | MODE = SHORT or $30k\Omega$ to GND |     | 311   |     | IVIHZ |  |

| Parallel Input Setup Time                    | ts∪                             | (Note 4)                           | -94 |       |     | ps    |  |

| Parallel Input Hold Time                     | tH                              | (Note 4)                           | 300 |       |     | ps    |  |

| PARALLEL CLOCK OUTPUT SPE                    | CIFICATIO                       | NS (PCLKO±)                        |     |       |     |       |  |

| Parallel Clock Output Rise/Fall<br>Time      | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%                         | 100 |       | 200 | ps    |  |

| Parallel Clock Output Duty Cycle             |                                 |                                    | 46  |       | 54  | %     |  |

| SERIAL OUTPUT SPECIFICATIO                   | NS (SDO±, S                     | SCLKO±)                            |     |       |     |       |  |

| Sorial Output Data Data                      |                                 | RATESET = GND                      |     | 2.488 |     | Chao  |  |

| Serial Output Data Rate                      |                                 | RATESET = $V_{CC}$                 |     | 2.666 |     | Gbps  |  |

| Serial Data Output Rise/Fall Time            | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%                         |     |       | 80  | ps    |  |

| Serial Output Clock to Data Delay            | tclk-q                          | (Note 5)                           | -25 |       | 25  | ps    |  |

**MAX3892**

### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ . Typical values are at  $V_{CC} = +3.3V$ , differential LVDS loads =  $100\Omega \pm 1\%$ , CML loads =  $50\Omega \pm 1\%$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Note 3)

| PARAMETER                                              | SYMBOL     | CONDITIONS         | MIN  | TYP | MAX | UNITS             |

|--------------------------------------------------------|------------|--------------------|------|-----|-----|-------------------|

| Serial Clock Output Jitter<br>Generation               | JG         | (Note 6)           |      | 1.2 | 1.4 | ps <sub>RMS</sub> |

| Serial Data Output Random Jitter                       | RJ         |                    |      |     | 1.4 | ps <sub>RMS</sub> |

| Serial Data Output Deterministic<br>Jitter             | DJ         | (Note 7)           |      |     | 19  | ps <sub>p-p</sub> |

| REFERENCE CLOCK INPUT SPE                              | CIFICATION | IS (RCLK)          |      |     |     |                   |

| Reference Clock Frequency<br>Tolerance                 |            |                    | ±100 |     |     | ppm               |

| Reference Clock Input Duty Cycle                       |            |                    | 30   |     | 70  | %                 |

| RESET INPUTS (RESET)                                   |            |                    |      |     |     |                   |

| Minimum Pulse Width of FIFO<br>Reset                   |            | UI is PCLKO period |      | 4   |     | UI                |

| Tolerated Drift Between PCLKI<br>and PCLKO After Reset |            | UI is PCLKO period |      | ±1  |     | UI                |

Note 1: Specifications at -40°C are guaranteed by design and characterization.

Note 2: Measured with SLBO/CLK622 and SCLK outputs disabled and CML outputs open.

Note 3: AC characteristics are guaranteed by design and characterization.

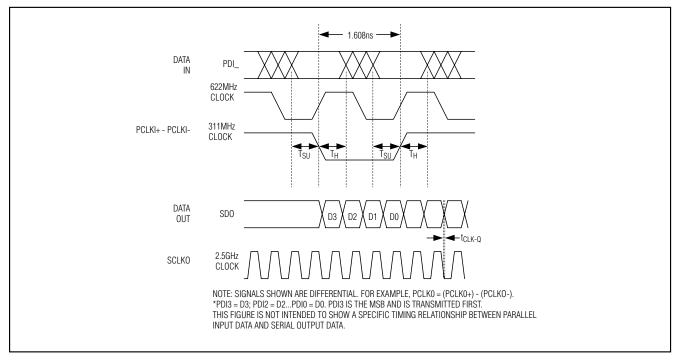

Note 4: In 622MHz clock mode, the parallel data is clocked in by the rising edge of the 622MHz/666MHz parallel clock input. In the 311MHz clock mode, the parallel data is clocked in on both the rising and falling edges of the clock. The parallel input setup and hold time increases by 60ps if the duty cycle is between 48% to 52% in 311MHz mode (Figure 1).

Note 5: Relative to the falling edge of the SCLKO.

**Note 6:** Measurement bandwidth is BW = 12kHz to 20MHz.

**Note 7:** Deterministic jitter includes pattern-dependent jitter and pulse-width distortion. Measured using a 2<sup>7</sup> - 1 PRBS pattern with 96 consecutive identical digits.

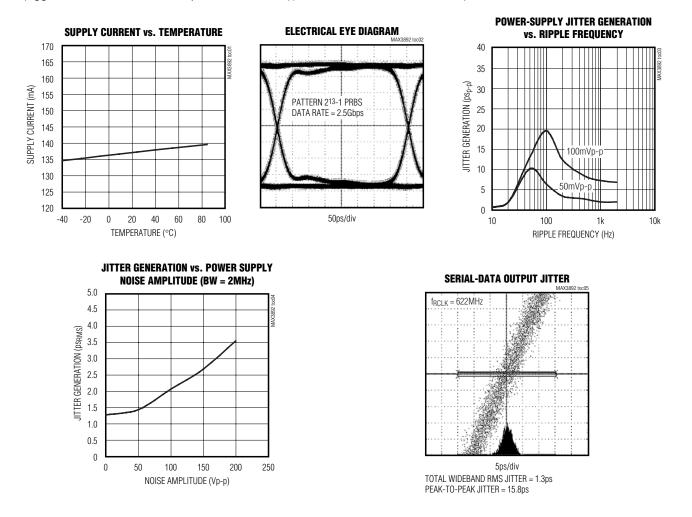

### **Typical Operating Characteristics**

(V<sub>CC</sub> = +3.3V, CML loads AC-coupled to  $50\Omega \pm 1\%$ , T<sub>A</sub> = +25°C, unless otherwise noted.)

### Pin Description

| PIN                      | NAME   | FUNCTION                                                                                                               |

|--------------------------|--------|------------------------------------------------------------------------------------------------------------------------|

| 1, 16, 22, 27,<br>33, 44 | GND    | Supply Ground                                                                                                          |

| 2, 5, 8, 11              | VCCO   | Supply Voltage for Outputs +3.3V. Add bypass capacitors near these pins before connecting to the $V_{CC}$ power plane. |

| 3                        | SCLKO- | Negative Serial Clock Output, CML 2.488GHz or 2.666GHz                                                                 |

| 4                        | SCLKO+ | Positive Serial Clock Output, CML 2.488GHz or 2.666GHz                                                                 |

| 6                        | SDO-   | Negative Serial Data Output, CML 2.488Gbps or 2.666Gbps                                                                |

| 7                        | SDO+   | Positive Serial Data Output, CML 2.488Gbps or 2.666Gbps                                                                |

### M/IXI/M

### Pin Description (continued)

| PIN            | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                          |

|----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9              | SLBO-             | Negative System Loop-Back Output or 622MHz/666MHz Clock Output. Select CML data or clock as shown in Table 1.                                                                                                                                                                                                     |

| 10             | SLBO+             | Positive System Loop-Back Output or 622MHz/666MHz Clock Output. Select CML data or clock as shown in Table 1.                                                                                                                                                                                                     |

| 12             | SLBPD             | System Loopback Power Down, TTL Input. SLPD = high activates the system loopback output driver; SLBPD = low powers down the loop-back output driver                                                                                                                                                               |

| 13             | SLBEN             | System Loop-Back Enable Input, TTL Input. SLBEN = high activates the system loop-back output; SLBEN = low activates the 622MHz/666MHz reference clock output.                                                                                                                                                     |

| 14             | RESET             | FIFO Reset, TTL Input. An active-high reset recenters the FIFO to tolerate maximum skew between PCLKI and PCLKO.                                                                                                                                                                                                  |

| 15             | FIFOERROR         | FIFO Error Indicator, TTL Output. Active high when the read/write clocks access the same FIFO address. This signal may be used to control RESET.                                                                                                                                                                  |

| 17, 28, 36, 41 | V <sub>CC</sub>   | Supply Voltage, +3.3V                                                                                                                                                                                                                                                                                             |

| 18             | LOL               | Loss of Lock, TTL Output. An active low indicates that the VCO and reference frequency differ by 500ppm.                                                                                                                                                                                                          |

| 19             | MODE              | Clock Control Input:<br>$MODE = GND$ ; $f_{PCLKI} = 311.04MHz/333MHz$ with SCLKO active<br>$MODE = 30k\Omega$ to GND; $f_{PCLKI} = 311.04MHz/333MHz$ with SCLKO off<br>$MODE = OPEN$ (float); $f_{PCLKI} = 622.08MHz/666MHz$ with SCLKO off<br>$MODE = V_{CC}$ ; $f_{PCLKI} = 622.08MHz/666MHz$ with SCLKO active |

| 20             | PCLKI+            | Positive Parallel Clock, LVDS Input. Data is written to the input register on the clock rising edge in 622Mbps mode and on both rising and falling edges in 311Mbps mode (Figure 1).                                                                                                                              |

| 21             | PCLKI-            | Negative Parallel Clock, LVDS Input (Figure 1).                                                                                                                                                                                                                                                                   |

| 23, 25, 29, 31 | PDI3+ to<br>PDI0+ | Positive Data Inputs, LVDS (622Mbps or 666Mbps)                                                                                                                                                                                                                                                                   |

| 24, 26, 30, 32 | PDI3- to<br>PDI0- | Negative Data Inputs, LVDS (622Mbps or 666Mbps)                                                                                                                                                                                                                                                                   |

| 34             | PCLKO+            | Positive Parallel Clock Output, LVDS. This clock may be 622.08MHz or 666MHz.                                                                                                                                                                                                                                      |

| 35             | PCLKO-            | Negative Parallel Clock Output, LVDS. This clock may be 622.08MHz or 666MHz.                                                                                                                                                                                                                                      |

| 37             | RCLK+             | Positive Reference Clock Input, LVPECL                                                                                                                                                                                                                                                                            |

| 38             | RCLK-             | Negative Reference Clock Input, LVPECL                                                                                                                                                                                                                                                                            |

| 39             | CLKSET            | Reference Clock Rate Programming Pin:<br>CLKSET = $V_{CC}$ ; RCLK = 622.08MHz/666MHz<br>CLKSET = OPEN (float); RCLK = 155.52MHz/167MHz<br>CLKSET = 30k $\Omega$ to GND; RCLK = 77.76MHz/83.3MHz<br>CLKSET = GND; RCLK = 38.88MHz/41.6MHz                                                                          |

| 40             | RATESET           | Data Rate Select, TTL Input. RATESET = high for 2.666Gbps, RATESET = low for 2.488Gbps.                                                                                                                                                                                                                           |

| 42             | FIL               | PLL Capacitor Pin. Connect a 0.1µF capacitor from this pin to VCCVCO.                                                                                                                                                                                                                                             |

| 43             | VCCVCO            | Supply Voltage for VCO +3.3V. Add bypass capacitors near this pin before connecting to the $V_{CC}$ power plane.                                                                                                                                                                                                  |

| EP             | Exposed<br>Paddle | The exposed paddle must be soldered to ground for proper thermal and electrical operation.                                                                                                                                                                                                                        |

M/XI/M

### **Detailed Description**

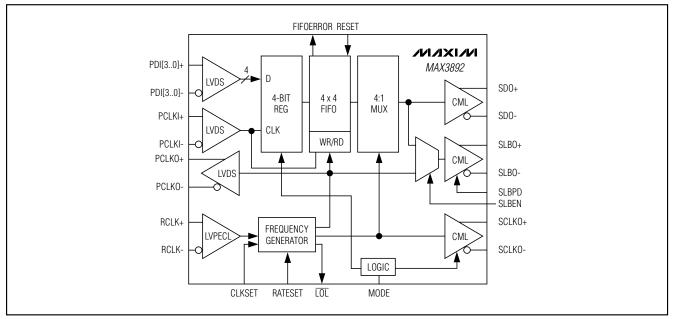

The MAX3892 converts 4-bit-wide, 622Mbps/667Mbps data to 2.5Gbps/2.7Gbps serial data (Figure 2). Data is loaded into the 4:1 MUX through a  $4 \times 4$ -bit FIFO buffer for wide tolerance to clock skew. Clock and data inputs are LVDS levels while high-speed serial outputs are CML. An internal PLL frequency synthesizer generates a serial clock from a low-speed reference clock.

### Low-Voltage Differential-Signal Inputs and Outputs

The MAX3892 has LVDS inputs and outputs for interfacing with high-speed digital circuitry. The LVDS standard is based on the IEEE 1596.3 LVDS specification. This technology uses differential low-voltage swings to achieve fast transition times, minimized power dissipation, and noise immunity. For proper operation, the parallel clock LVDS outputs (PCLKO+, PCLKO-) require 100 $\Omega$  differential DC termination between the positive and negative outputs. Do not terminate these outputs to ground. The parallel data and parallel clock LVDS inputs (PDI+, PDI-, PCLKI+, PCLKI-) are internally terminated with 100 $\Omega$  differential input resistance, and therefore do not require external termination.

### **PECL Inputs**

The reference clock (RCLK+, RCLK-) has PECL inputs for interfacing to a crystal oscillator with AC or DC connections. The RCLK inputs are self-biasing to V<sub>CC</sub> - 1.3V for AC-coupled inputs. Only a 100 $\Omega$  differential termination resistance must be added when inputs are AC-coupled.

### **Current-Mode Logic Outputs**

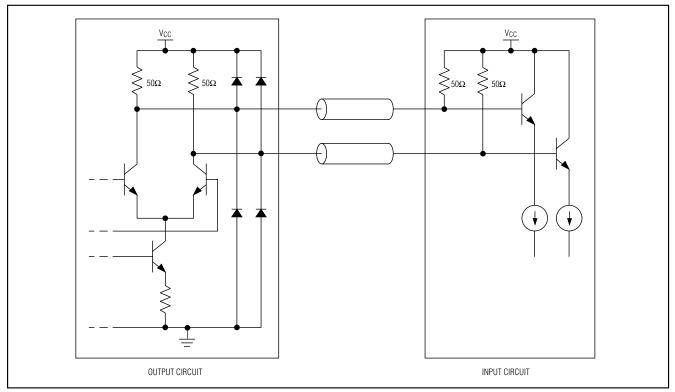

The 2.5Gbps/2.7Gbps data, clock, and system loopback outputs (SDO+, SDO-, SCLKO+, SCLKO-, SLBO+, SLBO-) of the MAX3892 are designed using current-mode logic (CML). The configuration of the MAX3892 CML output circuit includes internal 50 $\Omega$ back termination to V<sub>CC</sub> (Figure 3). These outputs are intended to drive a 50 $\Omega$  transmission line terminated with a matched load impedance.

### **FIFO Buffer**

Data is latched into the MAX3892 by the parallel input clock PCLKI. The parallel input clock serves as the FIFO write clock. The parallel output clock PCLKO acts as the FIFO read clock that loads the 4:1 MUX. The FIFO allows the read and write clocks to vary by up to  $\pm 10$ I. Conditions that result in the read and write clock accessing the same FIFO address are indicated by

Figure 1. Timing Diagram

| N  |

|----|

| 5  |

| 00 |

| 3  |

| ×  |

| d  |

|    |

|    |

### Table 1. Loop-Back Operation Mode

| SLBPD           | SLBEN           | SLBO $\pm$ OUTPUT                          |

|-----------------|-----------------|--------------------------------------------|

| VIL             | Х               | Power-Down SLBO Output                     |

| VIH             | VIL             | 622MHz/667MHz Clock<br>Output              |

| V <sub>IH</sub> | V <sub>IH</sub> | 2.5Gbps/2.7Gbps System<br>Loop-Back Output |

# Table 2. Setting the Reference ClockFrequency

| CLKSET              | RATESET         | RCLK± FREQUENCY (MHz) |

|---------------------|-----------------|-----------------------|

| Vcc                 | V <sub>CC</sub> | 666                   |

| VCC                 | GND             | 622                   |

| OPEN                | V <sub>CC</sub> | 166.5                 |

| OPEN                | GND             | 155.52                |

| 30k $\Omega$ to GND | V <sub>CC</sub> | 83.25                 |

| 30K22 10 GIND       | GND             | 77.76                 |

| GND                 | V <sub>CC</sub> | 41.63                 |

| GND                 | GND             | 38.88                 |

latching high FIFOERROR. To clear this condition, RESET must be asserted high for at least 4UI. FIFOER-ROR may be tied directly to the RESET input to recenter the FIFO. After reset, the full elastic range of the FIFO is available again.

### **Frequency Synthesizer**

The PLL synthesizes a 2.5Gbps/2.7Gbps clock (SCLKO) from an external reference clock. The PLL reference clock (RCLK) may be 622.08MHz/666.53MHz, 155.52MHz/166.6MHz, 77.76MHz/83.3MHz or 38.88MHz/41.65MHz as determined by CLKSET and RATESET. See Table 2 for the reference frequency selection. The parallel output clock PCLKO is also derived from the synthesizer to be SCLKO divided by 4. A TTL-compatible loss-of-lock indicator, LOL, goes low when the VCO is unable to lock to the reference frequency. Frequency difference on RCLK with respect to the divided down SCLKO greater than 500ppm is indicated by a low state on LOL. When the frequency difference between the clocks is less than 250ppm, LOL high indicates a lock condition.

### System Loopback

The MAX3892 is designed to allow system loop-back testing. The loop-back outputs (SLBO+, SLBO-) of the MAX3892 may be directly connected to the loop-back inputs of a deserializer (such as the MAX3882) for system diagnostics. Alternatively, the SLBO pins can be programmed to provide a 622MHz reference clock.

# Table 3. Setting the Clock Mode

| MODE       | RATESET         | PCLKI±<br>FREQUENCY<br>(MHz) | SCLKO±<br>FREQUENCY<br>(GHz) |

|------------|-----------------|------------------------------|------------------------------|

| Vee        | V <sub>CC</sub> | 666Hz                        | 2.666                        |

| Vcc        | GND             | 622Hz                        | 2.488                        |

|            | Vcc             | 666Hz                        | Disabled                     |

| OPEN       | GND             | 622Hz                        | Disabled                     |

| 30kΩ<br>to | V <sub>CC</sub> | 333Hz                        | Disabled                     |

| GND        | GND             | 311Hz                        | Disabled                     |

|            | Vcc             | 333Hz                        | 2.666                        |

| GND        | GND             | 311Hz                        | 2.488                        |

This reference clock can provide a clock hold-over signal to a clock and data recovery (CDR) circuit in the event of loss of signal (LOS).

### \_Design Procedure

### **Clock Mode Selection**

The frequencies of the MAX3892 can be set up using CLKSET, RATESET, and MODE as shown in Tables 2 and 3.

### Layout Techniques

For best performance, use good high-frequency layout techniques. Filter voltage supplies and keep ground connections short. Use multiple vias where possible. Also, use controlled-impedance transmission lines to interface with the MAX3892 clock and data inputs and outputs.

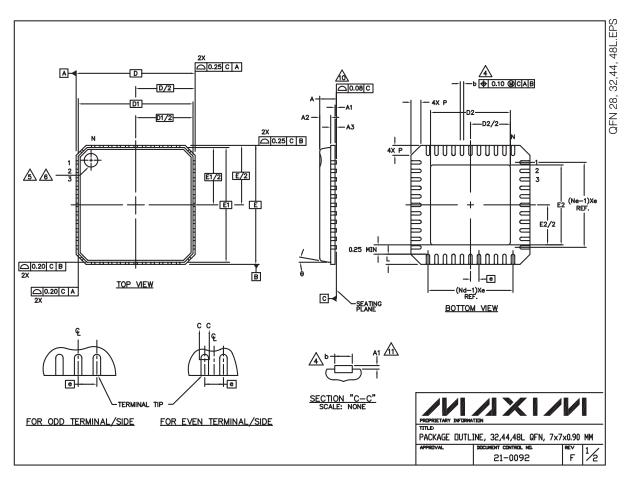

### **Exposed-Pad Package**

The EP 44-pin QFN incorporates features that provide a very low thermal-resistance path for heat removal from the IC to a PC board. The MAX3892's EP must be soldered directly to a ground plane with good thermal conductance.

Figure 2. Functional Diagram

Figure 3. Current-Mode Logic

**M**XX/M

Figure 4. Differential Output Levels

### **Pin Configuration**

### \_Chip Information

TRANSISTOR COUNT: 6210

### Package Information

### \_Package Information (continued)

### NOTES:

MAX3892

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM(.012 INCHES MAXIMUM) 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. - 1994. 3. N IS THE NUMBER OF TERMINALS. Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION. 4. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- ▲ THE PIN #1 IDENTIFIER MUST EXIST ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/ LASER MARKED. OF PACKAGE BODY.

- 6 EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.08mm.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

- EXCLUDE EMBEDDED PART OF EXPOSED PAD FROM MEASURING. 10. MEETS JEDEC M0220.

- 11. THIS PACKAGE OUTLINE APPLIES TO ANVIL SINGULATION (STEPPED SIDES) AND TO SAW SINGULATION (STRAIGHT SIDES) QFN STYLES.

| S<br>Y            |           | COMMON |      |                   |  |  |  |  |  |  |

|-------------------|-----------|--------|------|-------------------|--|--|--|--|--|--|

| ,×∎®0-            | DI        | No     |      |                   |  |  |  |  |  |  |

| ۹Ľ                | MIN.      | NOM.   | MAX. | ] <sup>-</sup> τε |  |  |  |  |  |  |

| Α                 | 0.80      | 0.90   | 1.00 |                   |  |  |  |  |  |  |

| A1                | 0.00      | 0.01   | 0.05 |                   |  |  |  |  |  |  |

| A2                | 0.00      | 0.65   | 1.00 |                   |  |  |  |  |  |  |

| A3                | 0.20 REF. |        |      |                   |  |  |  |  |  |  |

| D<br>D1           |           |        |      |                   |  |  |  |  |  |  |

| D1                | 6.75 BSC  |        |      |                   |  |  |  |  |  |  |

| Ε                 | 7.00 BSC  |        |      |                   |  |  |  |  |  |  |

| E<br>E1<br>Ø<br>P | 6.75 BSC  |        |      |                   |  |  |  |  |  |  |

| Φ                 | 0°        |        | 12°  |                   |  |  |  |  |  |  |

|                   | 0         |        | 0.60 |                   |  |  |  |  |  |  |

| D2                | 2.25      | -      | 5.25 |                   |  |  |  |  |  |  |

| E2                | 2.25      | -      | 5.25 |                   |  |  |  |  |  |  |

| S<br>¥<br>80- | PITCH VARIATION C |          |      | No <sub>7</sub> | O.BEL <sup>4</sup> S | PITCH VARIATION C |          |      | <sup>Н</sup> о <sub>те</sub> | -0.8E <sup>-4</sup> | PITCH VARIATION D |          |      | н <sub>оте</sub> |

|---------------|-------------------|----------|------|-----------------|----------------------|-------------------|----------|------|------------------------------|---------------------|-------------------|----------|------|------------------|

| e             |                   | 0.65 BSC |      | <u> </u>        | e                    |                   | 0.50 BSC |      | <u> </u>                     | e                   |                   | 0.50 BSC |      | -                |

| N             | 32                |          |      | 3               | N                    | 44                |          |      | 3                            | N                   | 48                |          |      | 3                |

| Nd            | 8                 |          |      | 3               | Nd                   | 11                |          |      | 3                            | Nd                  | 12                |          |      | 3                |

| Ne            | 8                 |          |      | 3               | Ne                   | 11                |          |      | 3                            | Ne                  | 12                |          |      | 3                |

|               | 0.35              | 0.55     | 0.75 |                 | L                    | 0.35              | 0.55     | 0.75 |                              |                     | 0.30              | 0.40     | 0.50 | $\square$        |

| Ь             | 0.23              | 0.28     | 0.35 | 4               | Ь                    | 0.18              | 0.23     | 0.30 | 4                            | Ь                   | 0.18              | 0.23     | 0.30 | 4                |

21-0092

F

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.